I ricercatori dimostrano la scala dei transistor ad allineamento di nanotubi di carbonio a livelli inferiori a sotto i nodi di 10 nm.

27 luglio 2023 caratteristica

Questo articolo è stato vagliato secondo il processo editoriale e le politiche di Science X. Gli editori hanno evidenziato i seguenti attributi garantendo la credibilità del contenuto:

- fattori verificati

- pubblicazione sottoposta a revisione tra pari

- fonte affidabile

- revisionato

da Ingrid Fadelli, Phys.org

I nanotubi di carbonio, grandi molecole cilindriche composte da atomi di carbonio ibridati disposti in una struttura esagonale, hanno recentemente attirato l'attenzione degli ingegneri elettronici. Grazie alla loro configurazione geometrica e alle vantaggiose proprietà elettroniche, queste molecole uniche potrebbero essere utilizzate per creare transistor a effetto di campo (FET) più piccoli che presentano elevate efficienze energetiche.

I FET basati su nanotubi di carbonio hanno il potenziale per superare i transistor più piccoli basati sul silicio, ma il loro vantaggio nelle implementazioni reali deve ancora essere dimostrato in modo conclusivo. Un recente articolo di ricercatori dell'Università di Pechino e di altre istituzioni in Cina, pubblicato su Nature Electronics, illustra la realizzazione di FET basati su nanotubi di carbonio che possono essere ridotti alle stesse dimensioni di un nodo tecnologico al silicio di 10 nm.

"I progressi recenti nel raggiungimento di array di nanotubi di carbonio semiconduttori ad alta densità su wafer ci hanno avvicinato un passo alla utilizzazione pratica dei nanotubi di carbonio nei circuiti CMOS", ha detto Phys.org Zhiyong Zhang, uno dei ricercatori che ha condotto lo studio. "Tuttavia, gli sforzi di ricerca precedenti si sono concentrati principalmente sulla riduzione delle dimensioni del canale o della lunghezza del gate dei transistor a nanotubi di carbonio, mantenendo grandi dimensioni di contatto, che non possono essere accettate per circuiti CMOS ad alta densità nelle applicazioni pratiche.

'Il nostro obiettivo principale di questo lavoro è esplorare la vera capacità di ridimensionamento degli array di nanotubi di carbonio utilizzando due parametri di merito nell'industria del silicio, ossia il passo del gate contattato e l'area di una cella SRAM a 6T, mantenendo al contempo i vantaggi prestazionali'."

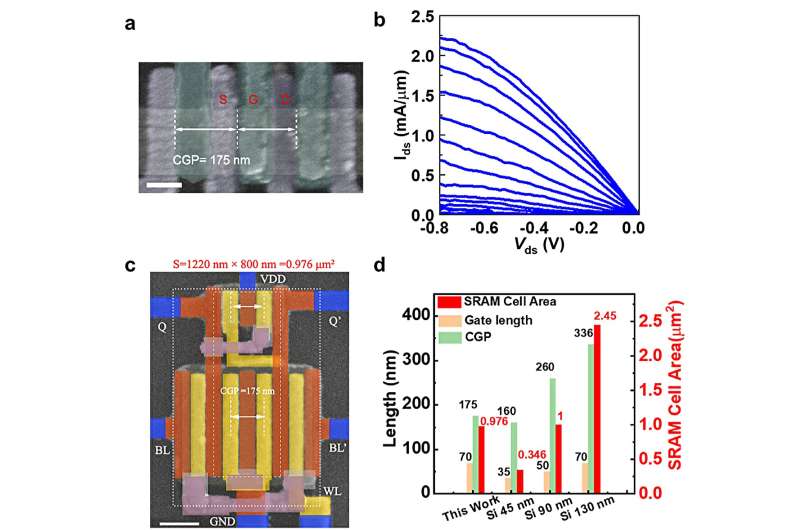

Zhang e i suoi colleghi si sono essenzialmente impegnati a dimostrare il valore pratico dei transistor a nanotubi di carbonio, mostrando che possono superare i FET convenzionali basati sul silicio con un passo di gate e un'area di cella SRAM a 6T paragonabile. Per fare ciò, hanno prima fabbricato FET basati su array di nanotubi di carbonio con un passo di gate contattato di 175 nm. Questo passo di gate è stato realizzato riducendo la lunghezza del gate e la lunghezza di contatto rispettivamente a 85 nm e 80 nm.

"Notevolmente, i transistor hanno mostrato una corrente di 2,24 mA/μm e una transconduttanza massima di 1,64 mS/μm, superando le prestazioni elettroniche dei transistor al nodo di silicio di 45 nm", ha detto Zhang. "Inoltre, una cella SRAM a 6T composta da questi transistor a nanotubi ultrariscalati è stata realizzata entro 1 μm2 e funziona correttamente. Abbiamo quindi investigato sul principale ostacolo, ossia la resistenza di contatto dei transistor a nanotubi di carbonio per ulteriore ridimensionamento."

Studi precedenti hanno mostrato che quando si segue uno schema di contatto diffuso noto come "contatto laterale", i portatori di carica possono essere iniettati solo dalla superficie dei nanotubi di carbonio. Ciò rende la resistenza dipendente dalla lunghezza dei nanotubi, limitando il grado di miniaturizzazione.

Per superare questo problema, Zhang e i suoi colleghi hanno introdotto un nuovo schema che chiamano "contatto completo". Questo schema prevede il taglio di entrambe le estremità dei nanotubi di carbonio prima di formare il contatto, permettendo così a parte dei portatori di carica di essere iniettati da queste estremità.

"Questo nuovo schema di contatto consente ai transistor a nanotubi di carbonio di essere ulteriormente ridotti con un passo del gate contattato inferiore a 55 nm, che corrisponde al nodo di tecnologia al silicio di 10 nm, superando i transistor al nodo di silicio di 10 nm grazie all'alta mobilità dei portatori di carica e alla velocità di Fermi", ha detto Zhang. "Il nostro lavoro ha dimostrato sperimentalmente una vera tecnologia a nodo di 90 nm mediante l'utilizzo dei nanotubi di carbonio, che possono essere resi geometricamente più piccoli e offrire prestazioni elettroniche superiori ai transistor al nodo di silicio di 90 nm."

Questo recente articolo introduce un approccio affidabile per ridurre le dimensioni dei transistor a nanotubi di carbonio, senza comprometterne le prestazioni. Fino ad ora, il team ha utilizzato la sua strategia per creare un transistor a nodo di 90 nm, ma ristrutturando la struttura dei contatti ritengono che questi transistor possano essere ridotti al di sotto di un nodo inferiore a 10 nm.

In futuro, il lavoro di Zhang e dei suoi colleghi potrebbe contribuire alla creazione di transistor a nanotubi di carbonio sempre più piccoli ed efficienti. Ciò potrebbe avere importanti implicazioni per lo sviluppo dell'elettronica.

'The next challenge that we are now tackling is to scale down the contact geometry for carbon nanotube n-type transistors to constructing complete CMOS technology, which is the necessary building blocks for modern digital ICs,' Zhang added.

'Currently, we use scandium for the contact of n-type carbon nanotube transistors. However, we are facing great difficulties as we scale down the contact length due to the oxidation of this low-work function metal. In addition, we are working to accurately characterize the interface quality between carbon nanotube arrays and high-κ dielectric, improving it to the level of silicon CMOS transistors to enhance gate controllability and reliability.'

Journal information: Nature Electronics

© 2023 Science X Network